Latencia CAS

Latencia CAS (del inglés column access strobe latency) es el tiempo (medido en número de ciclos de reloj) que transcurre entre que el controlador de memoria ha finalizado de seleccionar una fila de uno de sus bancos y, tras activar la selección de columna, el dato queda disponible en el bus de datos, o grabado si es una operación de escritura

Los datos son almacenados en celdas de memoria individuales, cada uno identificado de manera única por banco de memoria, fila y columna. Para tener acceso al DRAM, los controladores primero seleccionan el banco de memoria, luego una fila (usando el RAS), luego una columna (usando el CAS) y finalmente solicitan leer los datos de la posición física de la celda de memoria. La latencia CAS es el número de ciclos de reloj que transcurren desde que la petición de datos es enviada hasta que los datos son transmitidos desde el módulo.

Al seleccionar una tarjeta de memoria RAM, cuanto menor sea la latencia CAS (dada la misma velocidad de reloj), mejor será el rendimiento del sistema. La RAM DDR debería tener una latencia CAS de aproximadamente 3 u, óptimamente, 2 (y más recientemente tan bajo como 1,5). La RAM DDR2 puede tener latencias en los límites de 3 a 5.

La comparación entre velocidades de reloj podría resultar engañosa. La latencia CAS sólo especifica el tiempo entre la petición y el primer bit obtenido. La velocidad de reloj especifica la latencia entre bits. Así, leyendo cantidades importantes de datos, una velocidad de reloj más alta puede ser más eficiente en la práctica, incluso con una latencia CAS mayor de 5.

Las memorias DDR3, cuyas velocidades de reloj rondan desde los 1.333 MHz a mayores, pasando por 1.600 y 2.000 MHz, tienen CAS que van de 6 a 9 generalmente. Una memoria con CAS 6 y 1.600 MHz tiene normalmente mayor precio que otra con CAS 9 y 1.600 MHz, independientemente de su capacidad (1 o 2 Gb, por ejemplo), esto es normal ya que a igual frecuencia un CAS inferior implica un rendimiento superior.

A finales de 2012, el estándar más utilizado es DDR3 a 1600 MhZ, muchos módulos admiten subir la velocidad muy por encima de los 2000 MhZ pero el precio suele dispararse, especialmente considerando que no se suele notar mucha diferencia en el rendimiento.

Latencia de memorias

[editar]Se denominan latencias de una memoria RAM a los diferentes retardos producidos en el acceso a los distintos componentes de esta. Estos retardos influyen en el tiempo de acceso a la memoria por parte de la CPU, el cual se mide en nanosegundos (10-9 s).

Resulta de particular interés en el mundo del overclocking el poder ajustar estos valores de manera de obtener el menor tiempo de acceso posible.

Estructura física de la memoria

[editar]La memoria está compuesta por un determinado número de celdas, capaces de almacenar un dato o una instrucción y colocadas en forma de tablero de ajedrez. En lugar de tener 64 posibles posiciones donde colocar piezas, tienen n posiciones. No solo existe un tablero, sino que existen varios. De esta forma la estructura queda en forma de tablero de ajedrez tridimensional.

Accesos a memoria

[editar]Cuando se desea acceder a la memoria, es imprescindible indicar el número de tablero, el número de fila dentro del tablero y el número de columna o celda dentro de esa fila, en ese orden.

El tiempo que tarda la memoria en colocarse en la posición necesaria es relativamente pequeño; sin embargo, son tantos los datos e instrucciones que se almacenan en la memoria, que al final el proceso puede llegar a hacerse lento.

Debido a que se van a leer/escribir muchas cosas de/en la memoria, se necesita un sistema que lea muchas celdas al mismo tiempo, sin transportar los datos de dichas celdas y a continuación transportar todos los datos a la vez (dato o instrucción, ya que es lo único que se almacena en la memoria). Este sistema de leer muchas celdas y después transportar es conocido como bus a ráfagas o burst.

Si por cada celda que se leyese, el dato/instrucción se transportara a su destino, la lectura/escritura de memoria sería un proceso demasiado lento.

Tipos de latencia

[editar]Existen varios tipos de latencia en las memorias. Las más importantes son:

- CAS: indica el tiempo que tarda la memoria en colocarse sobre una columna o celda.

- RAS: indica el tiempo que tarda la memoria en colocarse sobre una fila.

- ACTIVE: indica el tiempo que tarda la memoria en activar un tablero.

- PRECHARGE: indica el tiempo que tarda la memoria en desactivar un tablero.

Lectura o escritura en memoria

[editar]El proceso a seguir cuando se desea leer o escribir en la memoria será el siguiente:

- Mandar una señal para activar el tablero y esperar a que termine el tiempo de activación (latencia ACTIVE).

- Mandar una señal para saber cuál es la fila en la que se debe posicionar y esperar a su latencia (latencia RAS).

- Mandar una señal para saber cuál es la columna o celda donde se debe posicionar y esperar (latencia CAS).

Tiempo de espera

[editar]El tiempo que tarda la memoria en proporcionar el dato es la suma de las tres latencias: ACTIVE, RAS y CAS.

Como se comenta anteriormente, antes de enviar el dato/instrucción a donde deba ir, se deben leer varias celdas de memoria. Por lo tanto, hay que pasar de una celda a otra, e ir esperando su correspondiente latencia CAS.

Si cada tablero tiene, por ejemplo, 64 celdas, y se van a leer 20 posiciones, las latencias totales a esperar son:

- 1 X ACTIVE (ya que se leen menos de 64 celdas, que son las que tiene el tablero completo)

- 3 X RAS (ya que cada fila tiene 8 posiciones)

- 20 X CAS (ya que se van a leer 20 celdas)

La latencia más importante, como queda patente, es la latencia CAS, y cuanto menor sea esta mejor rendimiento tendrá el ordenador en general.

Tiempo real

[editar]Sea una placa base con bus frontal o FSB a 200 MHz, el tiempo de cada ciclo de reloj es: F = 1 / T --> 200 * 10^6 = 1 / T --> T = 1 / 200 * 10^6 --> T = 5 * 10^-9 s = 5 nanosegundos

NOTA: las antiguas memorias RAM que empleaban los Pentium I eran de 70 ns. Las EDO, que eran las mismas un poco evolucionadas, eran de 60 ns. Así, se puede calcular con bastante facilidad el fsb de aquellos sistemas. Las primeras SDRAM que aparecieron, las PC 100, eran de 10 ns. Evidentemente, el FSB de aquellos sistemas era de 100 MHz.

En función de la calidad de las memorias, sus latencias serán mejores o peores.

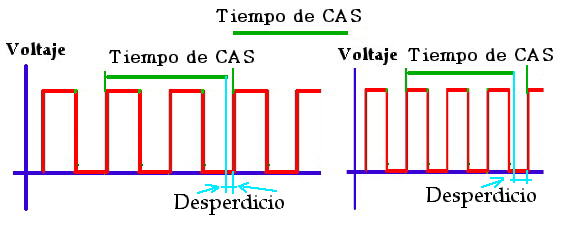

En la imagen se ve que la memoria tarda 12.5 ns en hacer el CAS. Si se cogen 3 ciclos (latencia CAS 3) sobran 2.5 ns. 2.5 en 15 es mucho, el 16.6%, y más aún teniendo en cuenta que se hacen muchísimos accesos a memoria. Por lo tanto, cuanto más tiempo se ahorre mejor.

Al hacer uso de la memoria DDR, se puede emplear tanto el flanco de subida como el de bajada para determinar la latencia, de modo que empleando CAS 2.5 este ejemplo sería óptimo.

Latencias vs FSB (caso práctico)

[editar]La diferencia de latencia es algo muy apreciable (en especial la latencia CAS) a la hora de medir el rendimiento del ordenador, ya que cuando se accede a memoria, tanto para leer como para escribir, se tiene que esperar por ella. Por cada celda del tablero que se lea hay que esperar la latencia CAS, por cada fila completa a la RAS, y por cada tablero diferente, a las ACTIVE y PRECHARGE (a veces se solapan). Se lee/escribe por ráfagas, pero en cada ráfaga se espera x veces a CAS, e y veces a RAS, siendo X = Y^2, ACTIVE, PRECHARGE, etc.

Por otra parte, cuanto más alto sea el FSB más rendimiento se obtiene. Aunque es una verdad a medias. Las latencias son inversamente proporcionales a la velocidad del bus FSB/HTT; es decir, cuanto mayor FSB maneje el sistema, peor latencia manejará y viceversa.

En el dibujo se pueden observar dos sistemas: uno con un FSB de 133 MHz (izquierda, no es de 100 MHz como dice en el dibujo; si no quedaría múltiplo directo del 200 MHz, y los lugares "de sobra", los desperdicios que ya veremos, coincidirían unos con otros) y otro, con un FSB de 200 MHz (derecha). Al tener mayor frecuencia, tenemos que en el mismo tiempo se hacen más ciclos. De ahí que a la derecha estén las “ondas” mucho más comprimidas. En ambos casos se emplea la misma memoria, que tarda un tiempo en hacer el acceso CAS. Este tiempo está marcado con una línea verde. La escala de tiempo en ambos casos es exactamente la misma, así que la línea verde será en ambos casos exactamente igual.

Para el sistema de la izquierda, se puede ver que la CAS de la memoria es de casi 2 ciclos. Para redondear, hay que redondear hacia arriba para darle tiempo a que termine; sobrará un poco. Sin embargo, para el caso de la derecha la CAS sería de 3.

En el último dibujo se ve que en la parte de la izquierda se pierde un poco de tiempo desde que se termina la CAS hasta que termina su latencia. Se ve el tiempo desperdiciado abajo a la derecha en color azul claro. Lo mismo pasa en el sistema del dibujo de la derecha. Pero en este caso es más tiempo (la escala temporal, eje de las abscisas, es la misma en ambos casos, por lo que el tiempo es mayor a la derecha).

En principio se podría pensar que aunque se pierda un poco más en un lado que en el otro, como el FSB es bastante superior en un lado que en el otro, seguro que es más rápido aún perdiendo un poco de tiempo en la CAS... A continuación se demuestra que esto no es cierto en todos los casos:

Veamos sistemas a 133 MHz, a 166 MHz y otro a 200 MHz, y empleando la misma, exactamente la misma, memoria en ambos casos. El tiempo que tarda en ejecutarse un ciclo:

- 1/133 * 10^6 = 7.5 * 10^-9 = 7.5 ns

- 1/166 * 10^6 = 6 * 10^-9 = 6 ns

- 1/200 * 10^6 = 5 * 10^-9 = 5 ns

Un ciclo en el sistema con bus a 200 MHz tarda 5 nanosegundos en ejecutarse, uno de 166 MHz tarda 6ns y 7.5 nanosegundos en el sistema con bus a 133 MHz.

Suponiendo que la memoria funciona en ambos sistemas con las siguientes latencias:

- Sistema 133 MHz --> 2 – 2 – 2 – 5 --> CAS, RAS, PRECHARGE y ACTIVE

- Sistema 166 MHz --> 3 – 2 – 2 – 5 --> CAS, RAS, PRECHARGE y ACTIVE

- Sistema 200 MHz --> 3 – 2 – 2 – 5 --> CAS, RAS, PRECHARGE y ACTIVE

Los tiempos que se tardaría en cada caso serían los siguientes:

- Sistema 133 MHz: (2 * 7.5) + (2 * 7.5) + (2 * 7.5) + (5 * 7.5) = 15 + 15 + 15 + 37.5 = 82.5 ns

- Sistema 166 MHz: (3 * 6) + (2 * 6) + (2 * 6) + (5 * 6) = 18 + 12 + 12 + 30 = 72 ns

- Sistema 200 MHz: (3 * 5) + (2 * 5) + (2 * 5) + (5 * 5) = 15 + 10 + 10 + 25 = 60 ns

Hasta aquí parecería que salen bien las cuentas, ya que el sistema con bus a 166 MHz tarda menos tiempo, 72 ns frente a 82.5 ns de uno de 133 MHz y más que uno de 200 MHz, que tarda sólo 60 ns.

Sin embargo, suponiendo que el tablero de la memoria es de 100 filas. Las cosas cambian.

Recordemos que la latencia CAS se ejecuta tantas veces como columnas haya, en este caso, 100 veces por cada vez que se ejecuta cambio de fila (RAS), por lo tanto, el cálculo justo, suponiendo que hay que leer en una ráfaga justo una fila entera quedaría de la siguiente manera:

- Sistema 133 MHz:

[100 * (2 * 7.5)] + (2 * 7.5) + (2 * 7.5) + (5 * 7.5) = (15 * 100) + 15 + 15 + 37.5 = 1500 ns + 67.5 ns = 1567.5 ns

- Sistema 166 MHz:

[100 * (3 * 6)] + (2 * 6) + (2 * 6) + (5 * 6) = (18 * 100) + 12 + 12 + 20 = 1800 ns + 54 ns = 1854 ns

- Sistema 200 MHz:

[100 * (3 * 5)] + (2 * 5) + (2 * 5) + (5 * 5) = (15 * 100) + 10 + 10 + 20 = 1500 ns + 50 ns = 1550 ns

Fíjense en el caso de 133 MHz contra el de 166 MHz. 1567.5 ns contra 1854 ns. ¿Una memoria de 133 MHz tarda menos en procesar que una de 166 MHz?. Este sería un caso extremo, que justo haya que leer una fila entera y no hubiera que hacer ni un solo salto de fila (RAS) ni cambios de tablero. Aunque aun así podría seguir siendo óptimo el caso del sistema con bus a 133.

Con ese cálculo queda clara la importancia de la latencia CAS con respecto a las demás, y la importancia de las latencias con respecto al bus FSB/HTT.