Transistor de electrón único

Concepto

[editar]El transistor de electron único (single-electron transistor, SET) es un dispositivo electrónico basado en el efecto Coulomb Blockade (CB). En este dispositivo el electrón se conduce de los terminales fuente/drenador a través de uniones túnel a un punto cuántico (isla conductiva). Se debe tener presente que el potencial de dicha isla conductiva se ve modificado por un tercer electrodo (puerta) que esta acoplado capacitivamente a la isla de conductiva.[1] La Fig. 1 muestra el esquema básico de un dispositivo SET, donde la isla conductiva esta comprendida entre las dos uniones túnel, que son modeladas por una capacidad (CD y CS) y una resistencia (RD y RS) en paralelo.

-

Fig. 1. Esquema de un SET.

Entorno de trabajo

[editar]El transistor de electrón único ha ganado recientemente interés con la creciente irrupción de la internet de las cosas (IoT) y las aplicaciones enfocadas a la salud; donde un consumo energético ultra-bajo es una condición importante. Entonces, para conseguir ambos retos que se le plantean a la nano-electrónica en este ámbito de trabajo: lograr bajos consumos y tener unas dimensiones en el rango nano-métrico para lograr así una mayor integración del dispositivo; el SET ha acontecido como un elemento muy interesante a tener en cuenta.

La mayor diferencia conceptual del SET respecto el MOSFET recae en el concepto de canal de conducción del dispositivo. Si bien, para el MOSFET el canal de conducción, que se genera entre fuente y drenador, conduce muchos electrones; por lo que respecta al SET el canal se hace a partir de una "isla de conducción" o punto cuántico (quantum dot, QD) donde la conducción es electrón a electrón.[2] Aprovechándose del fenómeno llamado "Coulomb blockade" la transferencia de electrones se puede hacer de forma individual, dado que la fuente y el drenador están separados por una unión túnel (tunnel junction). La investigación sobre el SET se basa principalmente en la "teoría ortodoxa" (orthodox theory) la cual se conlleva tres presunciones:

- Se ignora la cuantificación de la energía del electrón dentro de los conductores, i.e. el espectro de energía se trata como a un continuo, hecho que es válido sólo si Ek << kBT.

- El tiempo (τt) que el electrón tarda en superar la barrera se asume como insignificante en comparación con otras escales temporales. Esta presunción es válida para barreras de túnel del ordren τt ~10-15 s.

- No se contempla la posibilidad que se produzcan procesos de túnel simultáneos (co-túnel). Este hecho es válido si la resistencia de todas las berreras túnel del sistema son mucho mayores a la resistencia cuántica(~26 kΩ), con el objetivo de confinar los electrones en la isla de conducción.

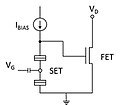

Los beneficios del uso de un SET, e.g. mayor integración y menor consumo, se ven contrarrestados por su bajo nivel de corriente y la necesidad de operar a bajas temperaturas (criogénicas). Esto puede conllevar que las variaciones térmicas puedan eliminar el efecto del Coulomb Blockade. Es por eso que la energía de carga electrostática (e2/C∑) debe ser superior a kBT, donde kB es la constante de Boltzmann y T es la temperatura. Esto implica que los valores de capacidad del QD es inversamente proporcional a la temperatura de operación. Para resolver este inconveniente se ha de considerar unos valores capacitivos relacionados con el SET por debajo de 1 aF, con el objetivo de validar su operatividad a temperatura ambiente. Cabe notar que la capacidad de la isla esta en función de sus dimensiones. Es por eso que para fabricar un SET operativo a temperatura ambiente la isla del SET debe ser menor a los 10 nm. Además, una de las ventajas del SET es que su proceso de fabricación es compatible con el de los dispositivos MOS, hecho que hace que puedan ser fabricados conjuntamente. Esto hace que sea interesante explorar la posibilidad de fabricar circuitos CMOS-SET,[3][4] con el objetivo de proporcionar un mayor nivel de corriente para los circuitos híbridos CMOS-SET (Fig. 2).

-

Fig. 2. Esquema del circuito híbrido SET-FET.

Cabe tener presente que la fabricación de dispositivos en el rango de dimensiones necesario para tener un SET operativo a RT no es trivial hecho que puede amenazar la viabilidad de fabricación de un SET.

Nuevas propuestas de fabricación

[editar]En el contexto de fabricar un SET operativo a RT, cabe destacar que recientemente la Unión Europea (EU) ha dado un impulso con la concesión de un proyecto de cuatro años centrado en la exploración de nuevas vías de fabricación de un SET, IONS4SET Archivado el 7 de junio de 2020 en Wayback Machine. (#688072). Este proyecto también busca la viabilidad de fabricar circuitos SET-FET operativos a temperatura ambiente. El principal objetivo es el diseño de un proceso de fabricación para a producir en masa los SET, hecho que podría extender el uso del circuito SET-FET. Cabe tener presente que para asegurar la operatividad a RT el punto cuántico debería ser menor a 5 nm y localizado entre fuente y drenador con unas uniones túnel de pocos nanómetros.[5] A día de hoy no existe un proceso de fabricación fiable, y es por eso de la importancia del proyecto que promueve la EU.

Referencias

[editar]- ↑ S. Mahapatra, V. Vaish, C. Wasshuber, K. Banerjee, and A. M. Ionescu, “Analytical Modeling of Single Electron Transistor for Hybrid CMOS-SET Analog IC Design,” IEEE Trans. Electron Devices, vol. 51, no. 11, pp. 1772–1782, Nov. 2004.

- ↑ K. Uchida, K. Matsuzawa, J. Koga, R. Ohba, S. I. Takagi, and A. Toriumi, “Analytical single-electron transistor (SET) model for design and analysis of realistic SET circuits,” Jpn. J. Appl. Phys., vol. 39, no. 4 B, pp. 2321–2324, 2000.

- ↑ A. M. Ionescu, S. Mahapatra, and V. Pott, “Hybrid SETMOS Architecture With Coulomb Blockade Oscillations and High Current Drive,” IEEE Electron Device Lett., vol. 25, no. 6, pp. 411–413, Jun. 2004.

- ↑ E. Amat, J. Bausells, and F. Perez-Murano, “Exploring the Influence of Variability on Single-Electron Transistors Into SET-Based Circuits,” IEEE Trans. Electron Devices, vol. 64, no. 12, pp. 5172–5180, Dec. 2017.

- ↑ F. Klupfel, A. Burenkov, J. Lorenz, "Simulation of silicon-dot-based single-electron memory devices," Int. Conf. SISPAD, pp. 237–240, 2016.

Enlaces externos

[editar][1] Archivado el 7 de junio de 2020 en Wayback Machine. IONS4SET web page.